- 您现在的位置:买卖IC网 > Sheet目录2001 > ISL35822LPIK (Intersil)IC CLOCK/DATA RECOVERY 192EBGA-B

12

8b/10b Coding and Decoding

8 Bit Mode

If 8B/10B encoding/decoding is turned on, the ISL35822

expects to receive a properly encoded serial bit stream. The

serial bit stream must be ordered “abcdeifghj” with “a” being

the first bit received and “j” the last. If the received data

contains an error, the Retimer will re-transmit it as an

ERROR or /E/ character. The character transmitted may be

controlled via the ERROR code Registers [3,4].C002’h,

encoding from, the FIFOs is listed in Table 1 below. If the

TRANS_EN bit or XAUI_EN bit (MDIO Registers at

all incoming XAUI or CX4/LX4 IDLE patterns will be

converted to the (internal) XGMII IDLE pattern set by the

respective PCS or PHY XS control registers at addresses

[3,4].C003’h, with a default value 107’h, the standard XGMII

The first full column of IDLES after any column containing a

non-IDLE will be stored in the respective elasticity FIFO, and

all subsequent full IDLE columns will repeat this pattern, until

another column containing a non-idle is received. If in

addition either of the AKR_SM_EN or XAUI_EN bits in the

respective MDIO registers at Addresses [3,4].C001’h is set

on transmission into a pseudo-random pattern of ||A||, ||K||,

and ||R|| codes according to the IEEE 802.3ae specified

algorithm. If neither of the AKR_SM_EN and XAUI_EN bits

are set, the internal IDLEs will all be transmitted as /K/

codes. Elasticity will be achieved by adding or deleting

columns of internal IDLEs.

If neither the TRANS_EN bit nor the XAUI_EN bit is set (for

either the PCS or the PHY XS), the incoming XAUI IDLE

codes will all be decoded to the appropriate XGMII control

code values in the respective internal FIFO. If the AKR_EN

or XAUI_EN bits are set, they will be sequenced into a

pseudo-random pattern of ||A||, ||K||, and ||R|| codes and

retransmitted, if not, the Inter Packet Gap (IPG) will be

retransmitted as the same XAUI codes as in the first full

IDLE column.

For most applications, the XAUI_EN bit high configuration is

the most desirable, and is the default.

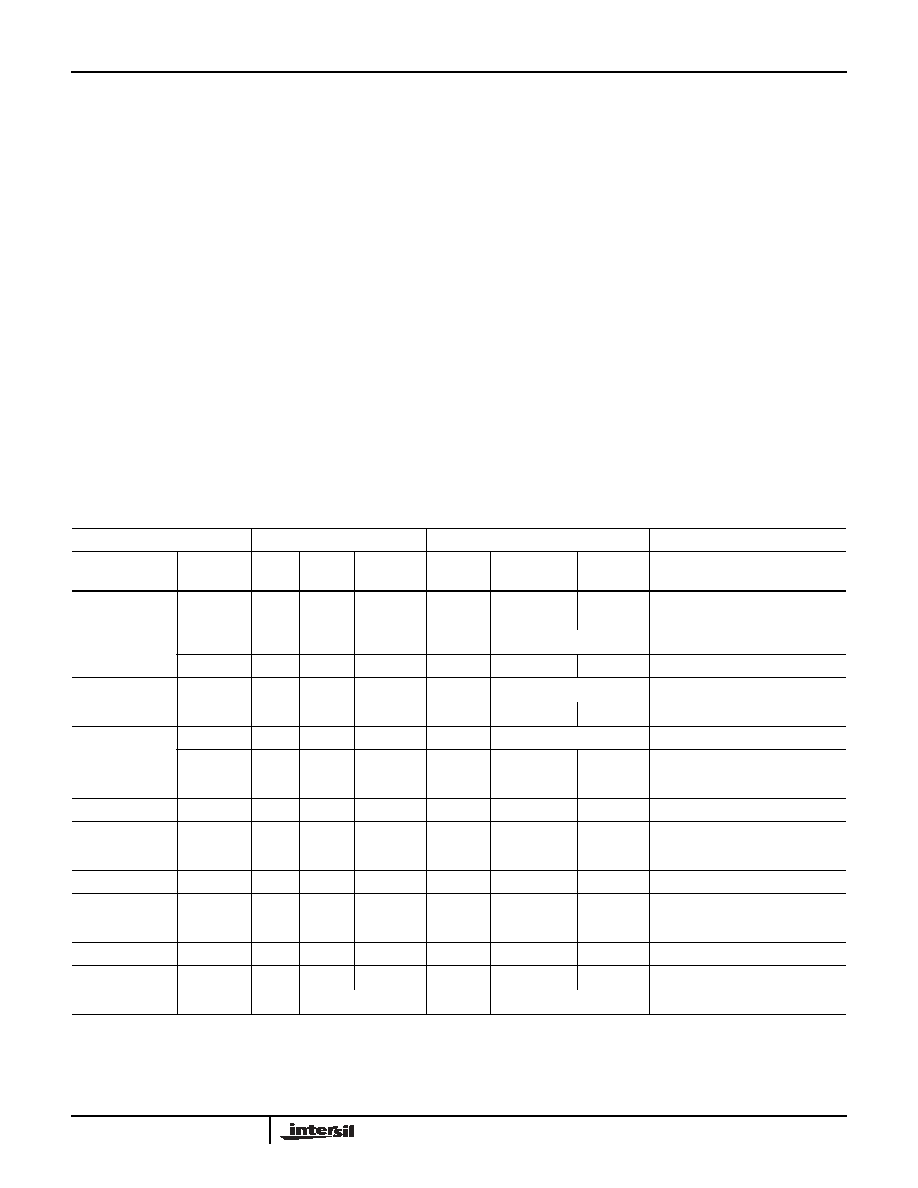

Table 1. VALID 10b/8b DECODER & ENCODER PATTERNS

RECEIVING SERDES

INTERNAL DATA

TRANSMITTING SERDES

NOTES

SERIAL CODE,

CHARACTER

TRANS_EN

BIT(4)

E-BIT

K-BIT

INTERNAL

FIFO DATA

AKR_SM_

EN(4)

SERIAL

CHARACTER

SERIAL

CODE

DESCRIPTION

Valid Data

X

0

0-FF’h

X

See 802.3

Table

Valid Data

Same Data Value as Received

/K/ (Sync) K28.5

1

0

1

07’h (2)

1

/A/ /K/ /R/

IEEE802.3ae algorithm

00

1

BC (1)

0

/K/

K28.5

Comma (Sync)

/A/ (Align) K28.3

1

0

1

07’h (2)

1

/A/ /K/ /R/

IEEE802.3ae algorithm

00

1

7C (1)

0

/A/

K28.3

Align

/R/ (Skip) K28.0

1

0

1

07’h (2)

1

/A/ /K/ /R/

IEEE802.3ae algorithm

00

1

1C (1)

0

/R/

K28.0

Alternate Idle (Skip)

/S/ K27.7

X

0

1

FB

1

/S/

K27.7

Start

/T/ K29.7

X

0

1

FD

0

/T/

K29.7

Terminate

K28.1

X

0

1

3C

X

K28.1

Extra comma

/F/ K28.2

X

0

1

5C

X

/F/

K28.2

Signal Ordered_Set

/Q/ K28.4

X

0

1

9C

X

/Q/

K28.4

Sequence Ordered_Set

K28.6

X

0

1

DC

X

K28.6

K28.7

X

0

1

FC

X

K28.7

Repeat has False Comma

K23.7

X

0

1

F7

X

K23.7

/E/ K30.7

X

1

FE

X

/E/

K30.7

Error Code

Any other

X

1

= ERROR reg.(3)

X

Invalid code

Error Code

Note (1): First incoming IDLE only, subsequent IDLEs in that block repeat first received code.

Note (2): Default value, actually set by ‘Internal Idle’ register, [3:4].C003’h, see Table 67 and Table 83.

Note (3): Value set by ‘ERROR Code’ register, [3:4].C002’h, see Table 66 and Table 66. The XAUI_EN bit forces it to 1FE’h.

Note (4): If the XAUI_EN bit is set, the ISL35822 acts as though both the TRANS_EN and AKR_EN bits are set.

ISL35822

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ISL41334IRZ-T7A

IC TXRX RS232/485 DL 2PRT 40QFN

ISL43485IB-T

IC TXRX 1TX/1RX 3V RS-485 8-SOIC

ISL51002CQZ-110

IC FRONT END 10BIT VID 128-MQFP

ISL5314IN

IC SYNTHESIZER DIGITAL 48-MQFP

ISL55100AIRZ-T

IC COMP DRVR/WINDOW 18V 72-QFN

ISL55100BIRZ

IC COMP DRVR/WINDOW 18V 72-QFN

ISL5627INZ

IC DAC DUAL 8BIT 3.3V 48-LQFP

ISL5629/2INZ

IC DAC 8BIT CMOS DUAL 48LQFP

相关代理商/技术参数

ISL36111

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:11.1Gb/s Lane Extender

ISL36111DRZ-EVALZ

功能描述:EVAL BOARD FOR ISL36111DRZ RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板

ISL36111DRZ-T7

功能描述:IC EQUALIZER REC 11.1GBPS 16QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:QLx™ 特色产品:NXP - I2C Interface 标准包装:1 系列:- 应用:2 通道 I²C 多路复用器 接口:I²C,SM 总线 电源电压:2.3 V ~ 5.5 V 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:剪切带 (CT) 安装类型:表面贴装 产品目录页面:825 (CN2011-ZH PDF) 其它名称:568-1854-1

ISL36111DRZ-TS

功能描述:IC EQUALIZER REC 11.1GBPS 16QFN RoHS:是 类别:集成电路 (IC) >> 接口 - 专用 系列:QLx™ 标准包装:3,000 系列:- 应用:PDA,便携式音频/视频,智能电话 接口:I²C,2 线串口 电源电压:1.65 V ~ 3.6 V 封装/外壳:24-WQFN 裸露焊盘 供应商设备封装:24-QFN 裸露焊盘(4x4) 包装:带卷 (TR) 安装类型:表面贴装 产品目录页面:1015 (CN2011-ZH PDF) 其它名称:296-25223-2

ISL36356A-APDK

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:PRISM 11Mbps Wireless Local Area Network Access Point

ISL36356A-APDK-EVAL

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:PRISM 11Mbps Wireless Local Area Network Access Point

ISL36411

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Quad Lane Extender

ISL36411DRZ-EVALZ

功能描述:EVAL BOARD FOR ISL36411DRZ RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:* 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板